| Version 8 (modified by sgupta, 15 years ago) (diff) |

|---|

WARP FPGA Board MGTs

The Virtex-4 FPGA is equipped with 10 pairs of differential multi-gigabit transceivers. The MGTs can support data rates of up to 6.5 Gbps including standards such as SATA, gigabit Ethernet and Infiniband. Each of these requires a different clock speed for best performance. On the FPGA Board three different connectors have been provided: SATA host and target, HSSDC2 jacks and SFP modules.

The MGTs on the FPGA are organized in two columns. Each column has two clock inputs and all the MGTs in the column can use either of those clocks. Our design maximizes the functionality by allowing the user to select the clock frequency that is input to the columns.

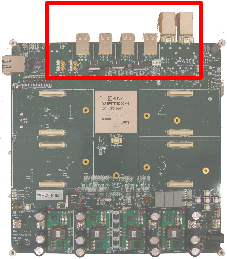

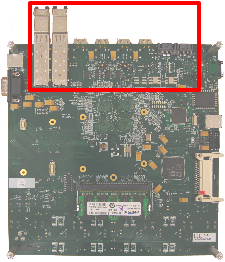

All the MGT connectors are located on the north side of the FPGA Board; both on the top and bottom.

MGT Connectors

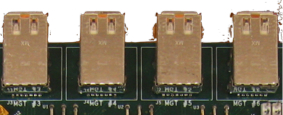

There are three types of MGT connectors on the board. Two Small form-factor Pluggable (SFP) occupy their own column. Four HSSDC2 connectors and two SATA occupy one column.

| MGT # | Type | Connector | MGT Tile | Column | LOC Constraint | TXP | TXN | RXP | RXN |

| 1 | SATA Target | J47 | 112B | 1 | GT11_X1Y4 | P1 | R1 | U1 | V1 |

| 2 | SATA Host | J46 | 112A | 1 | GT11_X1Y5 | M1 | N1 | J1 | K1 |

| 3 | HSSDC2 | J3 | 113B | 1 | GT11_X1Y6 | A4 | A3 | C1 | D1 |

| 4 | HSSDC2 | J4 | 113A | 1 | GT11_X1Y7 | A6 | A5 | A9 | A8 |

| 5 | HSSDC2 | J5 | 114B | 1 | GT11_X1Y8 | A14 | A13 | A11 | A10 |

| 6 | HSSDC2 | J6 | 114A | 1 | GT11_X1Y9 | A16 | A15 | A19 | A18 |

| 7 | SFP #1 | J49 | 102A | 0 | GT11_X0Y7 | A34 | A35 | A31 | A32 |

| 8 | SFP #2 | J48 | 102B | 0 | GT11_X0Y6 | A36 | A37 | C39 | D39 |