WARP v3 User Guide: Debug Header

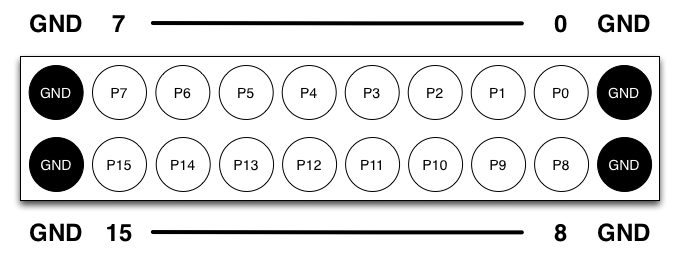

The WARP v3 board includes a generic debug header with 16 pins tied directly to FPGA I/O. The header itself has 20 pins. The four corner pins are tied to ground.

The 16 I/O pins are tied to FPGA I/O in a bank with VCCO = 2.5v.

| These pins are not 3.3v compatible! You must use external level shifting to interface with non-2.5v signals. |

The FPGA pin assignment for each debug pin is listed in the UCF snippet below:

#Debug header NET "DEBUGHDR<0>" LOC = "AG27" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<1>" LOC = "AE26" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<2>" LOC = "AF26" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<3>" LOC = "AD25" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<4>" LOC = "V24" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<5>" LOC = "AA23" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<6>" LOC = "AH30" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<7>" LOC = "AK31" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<8>" LOC = "AG28" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<9>" LOC = "AE27" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<10>" LOC = "AF28" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<11>" LOC = "AJ29" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<12>" LOC = "AH29" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<13>" LOC = "AL30" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<14>" LOC = "AM31" | IOSTANDARD = "LVCMOS25"; NET "DEBUGHDR<15>" LOC = "AP32" | IOSTANDARD = "LVCMOS25";

Last modified 11 years ago

Last modified on May 14, 2013, 1:55:09 PM

Attachments (1)

- Debug_Header_Diagram_BnW.png (27.8 KB) - added by welsh 11 years ago.

Download all attachments as: .zip